首页>>行业新闻>>

超越7nm!欧盟启动5G芯片CMOS工艺研究

欧盟(E.U.)最近启动一项为期三年的“为下一代高性能CMOS SoC技术整合III-V族纳米半导体”(INSIGHT)研发计划,这项研发经费高达470万美元的计划重点是在标准的互补金属氧化物半导体(CMOS)上整合III-V族电晶体通道。其最终目的则在于符合未来的5G规格要求,以及瞄准频宽更广、影像解析度更高的雷达系统。

除了IBM (瑞士),该计划将由德国弗劳恩霍夫应用固态物理研究所Fraunhofer IAF、法国LETI、瑞典隆德大学(Lund University)、英国格拉斯哥大学(University of Glasgow)以及爱尔兰丁铎尔国家研究所(Tyndall

National Institute)等组织联手进行。

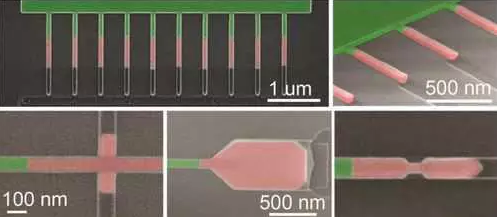

采用IBM模板辅助选择性外延(TASE)技术制造的单晶结构图——矽晶部份是绿色,III-V族半导体以红色表示(来源:IBM)

以IBM与隆德大学为主导的这项计划可分为两个阶段,IBM专注于传统平面电晶体原型与III-V族通道,而隆德大学则将深入研究垂直III-V族电晶体通道的可用性。

“首先,合作伙伴们将先共同确定水平或垂直电晶体原型是否最具有远景,”IBM的科学家Lukas Czornomaz介绍,“接着,我们将联手在三年计划届满以前推出一款射频(RF)测试电路,例如功率放大器(PA)。”

IBM有信心其平面方法将可发挥效用,因为该公司已经在一份去年发表的研究报告(该报告主题为IBM Scientists Present III-V Epitaxy and Integration to

Go Below 14nm)中证实了这一途径在14nm及其后的可行性。

IBM的工艺途径是透过其所谓的“模板辅助选择性外延”(TASE)技术。研究人员在矽基板上得以相容前闸极(gate-first)

CMOS的理想III-V族电晶体通道所在位置生长氧化物铜丝。接着再用III-V材料涂布纳米线,使其仅在1纳米级或埃级的区域接触基板。最后,研究人员从III-V涂布纳米线内部移去氧化层,因而使III-V族纳米管电晶体通道准确地位于正确位置。

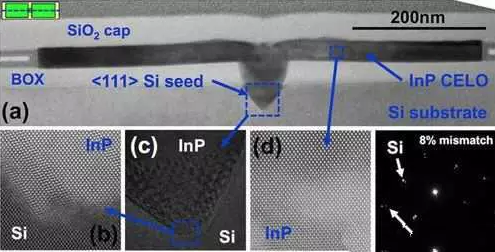

(a)采用IBM技术整合于矽晶上的III-V族半导体横截面图。由堆叠断层组成的晶种区(b,c)存在较多缺陷,而远离晶种区域可观察到完美晶格结构——未与矽晶匹配的部份仅8%,呈现完全松弛的III-V结构(d,e)(来源:IBM)

IBM预期,毫米波(mmWave)的RF性能功耗水准比目前更低得多,不仅可用于促进5G进展,同时还可用于认知电脑、下一代物联网(IoT)以及基于云端的支援平台。

INSIGHT计划的既定目标在于使CMOS扩展到超越7nm节点以后,从而开启一个以超高性能SoC服务为基础的全新应用范围。除了IBM与隆德大学,包括Fraunhofer、LETI、格拉斯哥大学与丁铎尔国家研究所等其他合作伙伴也分别为这项计划贡献在III-V族CMOS方面的专业知识与技术。

时间:2016-06-07